模擬CMOS集成電路設(shè)計(jì) EE618課程精要與實(shí)踐探索

模擬CMOS集成電路設(shè)計(jì)是現(xiàn)代電子工程領(lǐng)域的核心技術(shù)之一,尤其在通信、傳感、醫(yī)療電子及電源管理等應(yīng)用中扮演著關(guān)鍵角色。EE618課程《CMOS模擬集成電路設(shè)計(jì)1》系統(tǒng)性地介紹了這一領(lǐng)域的基礎(chǔ)理論與設(shè)計(jì)方法,為學(xué)習(xí)者奠定了從理論到實(shí)踐的堅(jiān)實(shí)基礎(chǔ)。

模擬集成電路設(shè)計(jì)的核心在于利用CMOS工藝實(shí)現(xiàn)信號(hào)的處理、放大、濾波及轉(zhuǎn)換等功能。與數(shù)字電路不同,模擬電路處理的是連續(xù)變化的電壓或電流信號(hào),對(duì)噪聲、非線性、功耗和工藝偏差等因素極為敏感。因此,設(shè)計(jì)者需深入理解器件物理特性、電路拓?fù)浣Y(jié)構(gòu)及系統(tǒng)級(jí)優(yōu)化策略。

EE618課程通常涵蓋以下核心內(nèi)容:

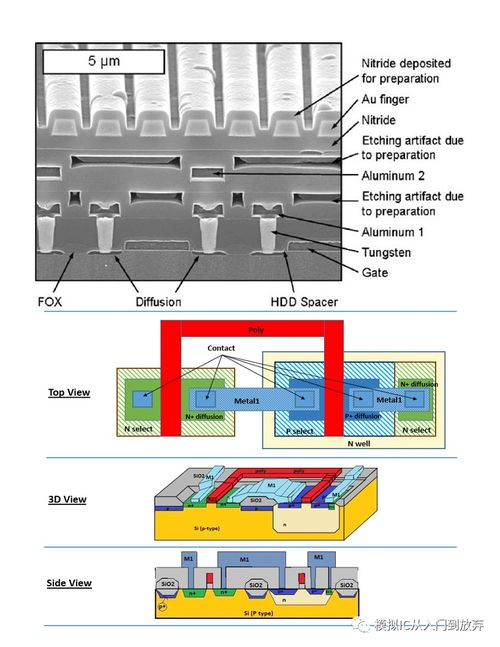

- MOSFET器件物理與模型:深入分析MOSFET在亞閾值區(qū)、飽和區(qū)及線性區(qū)的工作特性,以及小信號(hào)模型、噪聲模型和非理想效應(yīng)(如溝道長(zhǎng)度調(diào)制、體效應(yīng)等),為電路設(shè)計(jì)提供準(zhǔn)確的器件級(jí)認(rèn)知。

- 單級(jí)放大器設(shè)計(jì):包括共源極、共柵極、共漏極(源極跟隨器)及共源共柵等基本結(jié)構(gòu),重點(diǎn)講解增益、帶寬、輸入輸出阻抗及噪聲性能的分析與優(yōu)化。

- 差分放大器與電流鏡:差分對(duì)作為模擬電路的核心模塊,其失調(diào)、共模抑制比(CMRR)及電源抑制比(PSRR)是關(guān)鍵設(shè)計(jì)指標(biāo);電流鏡則廣泛用于偏置和主動(dòng)負(fù)載,匹配性與輸出阻抗是設(shè)計(jì)重點(diǎn)。

- 頻率響應(yīng)與穩(wěn)定性:通過(guò)極點(diǎn)-零點(diǎn)分析、波特圖及米勒效應(yīng)等方法,評(píng)估電路的帶寬和相位裕度,并引入補(bǔ)償技術(shù)(如米勒補(bǔ)償)以確保穩(wěn)定性。

- 噪聲分析:理解熱噪聲、閃爍噪聲等來(lái)源,計(jì)算電路的等效輸入噪聲,并在低噪聲設(shè)計(jì)中平衡功耗與性能。

- 反饋理論:反饋能改善電路增益精度、線性度及阻抗特性,但可能影響穩(wěn)定性,需細(xì)致分析反饋網(wǎng)絡(luò)的類型與效應(yīng)。

- 運(yùn)算放大器設(shè)計(jì):作為模擬系統(tǒng)的基石,課程會(huì)引導(dǎo)學(xué)習(xí)者設(shè)計(jì)兩級(jí)或折疊共源共柵運(yùn)放,并優(yōu)化增益、帶寬、擺率及功耗等參數(shù)。

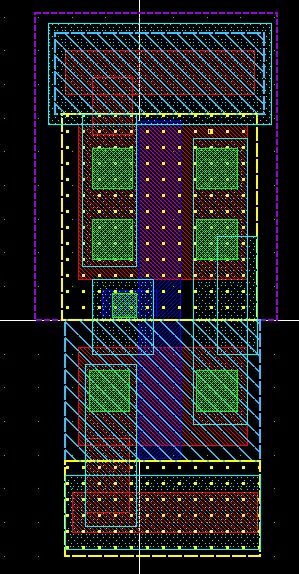

- 版圖設(shè)計(jì)與工藝考量:介紹匹配布局、寄生參數(shù)控制、閂鎖效應(yīng)預(yù)防及設(shè)計(jì)規(guī)則檢查(DRC)等實(shí)用技能,確保電路在硅片上的可靠實(shí)現(xiàn)。

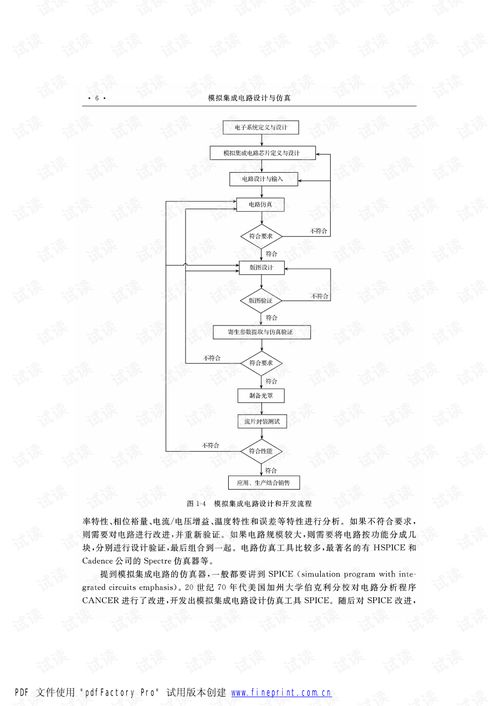

實(shí)踐環(huán)節(jié)是EE618課程不可或缺的部分。學(xué)生通常使用EDA工具(如Cadence Virtuoso)進(jìn)行電路仿真、版圖繪制和后仿真驗(yàn)證,從而將理論應(yīng)用于實(shí)際設(shè)計(jì)。例如,設(shè)計(jì)一個(gè)滿足特定增益和帶寬要求的運(yùn)算放大器,需經(jīng)歷電路構(gòu)思、直流偏置設(shè)置、交流特性仿真、瞬態(tài)響應(yīng)測(cè)試及版圖實(shí)現(xiàn)的全流程,這一過(guò)程深化了對(duì)設(shè)計(jì)折衷(如速度-精度-功耗權(quán)衡)的理解。

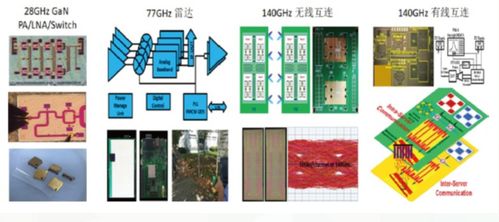

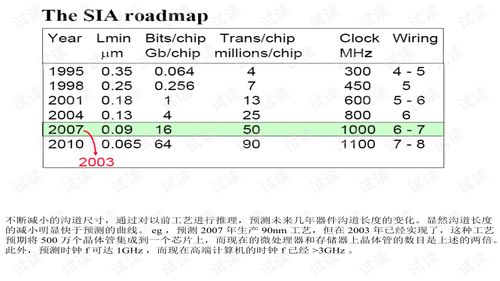

EE618《CMOS模擬集成電路設(shè)計(jì)1》不僅傳授了關(guān)鍵電路模塊的分析與設(shè)計(jì)方法,更培養(yǎng)了系統(tǒng)化工程思維。隨著工藝節(jié)點(diǎn)不斷縮小,模擬設(shè)計(jì)面臨新挑戰(zhàn)(如電源電壓降低、器件變異增大),但基礎(chǔ)原理始終是創(chuàng)新的源泉。掌握本課程內(nèi)容,將為從事高性能模擬IC、混合信號(hào)系統(tǒng)乃至射頻電路設(shè)計(jì)開(kāi)啟堅(jiān)實(shí)的大門(mén)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.xb1h.com/product/75.html

更新時(shí)間:2026-03-21 06:24:24